Verilog Data Types - ChipVerify

The primary intent of data-types in the Verilog language is to represent data storage elements like bits in a flip-flop and transmission elements like wires that connect between logic gates and sequential structures.

Why time data type is 4-state? - Verification Academy

Aug 28, 2019 · The time datatype is 4-state because Verilog only had 4-state integers. In Verilog, time and integer were similar types except that their size were platform dependent. SystemVerilog fixed time as a 64-bit unsigned integer, and integer as 32-bits.

Time Datatype - Chipdemy

The time datatype in verlog serves to measure the current simulation time in the context of debugging. This data type is particularly relevant in fields such as electronics, and simulations, where tracking the progression of time is crucial for understanding how systems behave.

Time and Realtime - SystemVerilog Tutorial - Verification Studio

In SystemVerilog, managing time and modeling real-time behavior is crucial, especially when simulating and verifying digital designs in the context of real-world timing. Two primary data types help achieve this: time and realtime. The time data type is used to represent simulation time.

Data Types in SV - VLSI Verify

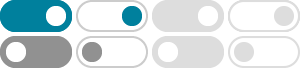

In Verilog behavior modeling, always, and initial procedural blocks use reg data type whereas, in dataflow modeling, continuous assignment uses wire data type. SystemVerilog allows driving signals in the ‘assign’ statements and procedural blocks using logic data type.

Verilog Data Types - GeeksforGeeks

Jun 14, 2022 · Some register data types are: reg, integer, time and real. reg is the most frequently used type. Reg is used for describing logic, integer for loop variables and calculations, real in system modules, and time and real-time for storing simulation times in test benches.

SystemVerilog Datatypes - Verification Guide

Time. Time is a 64-bit quantity that can be used in conjunction with the $time system task to hold simulation time. Time is not supported for synthesis and hence is used only for simulation purposes. Syntax. time time_variable_name; Parameters. Parameters represent constants, hence it is illegal to modify their value at runtime. However ...

What are the different types of data types in Verilog?

Jun 15, 2023 · Time: Verilog provides time data types to represent time values. These types are used to specify delays or timing constraints within a design. Reg: Verilog employs reg data types to store values until they are updated or changed.

Time datatype code - Chipdemy

Verilog doesn’t have a native time data type like it does for integer or real. Time delays and timing-related operations in Verilog are typically specified using time literals or constants. However, here are some examples that involve time delays and simulations:

Data Types - CS6102 Spring 2024-25

When you're implementing a digital circuit in hardware using Verilog, you'll be using data types like wires (wire), registers (reg), vectors, and memory (reg [N:0] mem [M];) extensively. These data types are used to model the behavior of actual …

- Some results have been removed