FIFO (computing and electronics) - Wikipedia

In computing and in systems theory, first in, first out (the first in is the first out), acronymized as FIFO, is a method for organizing the manipulation of a data structure (often, specifically a data buffer) where the oldest (first) entry, or "head" of the queue, is processed first.

First-in first-out memories (FIFOs) have progressed from fairly simple logic functions to high-speed buffers incorporating large blocks of SRAM. This application report takes a detailed look at the evolution of FIFO device functionality and at the architecture and applications of FIFO devices from Texas Instruments (TI ).

What is a FIFO? - Surf-VHDL

Apr 23, 2016 · FIFO means First-In First-Out. A FIFO is a structure used in hardware or software application when you need to buffer a data. Basically, you can think about a FIFO as a bus queue in London. The people that arrive first is the one who catch the bus first….

Synchronous FIFO - VLSI Verify

FIFO can store/write the wr_data at every posedge of the clock based on wr_en signal till it is full. The write pointer gets incremented on every data write in FIFO memory. The data can be taken out or read from FIFO at every posedge of the clock based on the rd_en signal till it is empty.

FIFO (First-In-First-Out) approach in Programming

Dec 6, 2022 · FIFO is an abbreviation for first in, first out. It is a method for handling data structures where the first element is processed first and the newest element is processed last. Real-life example:

FIFO Memory Selection Guide: Types, Features, Applications

Oct 30, 2024 · FIFO memory varies in terms of density, number of words, bits per word, supply voltage, and operating temperature. The density is the capacity of the chip in bits. The number of words equals the number of rows, each of which stores a memory word and connects to a word line for addressing purposes.

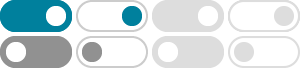

What is FIFO? | Synchronous FIFO | Asynchronous FIFO

Apr 9, 2021 · A Synchronous FIFO is a First-In-First-Out queue in which there is a single clock pulse for both data write and data read. In Synchronous FIFO the read and write operations are performed at the same rate.

Cache Algorithms: FIFO vs. LRU vs. LFU – A Comprehensive Guide

In this comprehensive guide, we’ll dive deep into three popular cache algorithms: FIFO (First-In-First-Out), LRU (Least Recently Used), and LFU (Least Frequently Used).

- [PDF]

Memory examples

FIFO Example Design a FIFO to store up to 256 data items of 16-bits each, using 256x 16-bit dual-port SSRAM for the data storage. Assume the FIFO will not be read when it is empty, not to be written when it is full, and that the write and read ports share a common clock. Digital Design —Chapter 5 —Memories 12

FIFO Design: A Comprehensive Guide | by Si D K | Jan, 2025

Jan 30, 2025 · First-In-First-Out (FIFO) memory design is a crucial component in digital systems for buffering data between different clock domains. In this project, we designed and implemented a...