– Learn the principles of digital design – Learn to systematically debug increasingly complex designs – Design and build digital systems – Learn what’s under the hood of an electronic …

2) Draw a complete and detailed timing diagram that enables the hardware in the pipelined block diagram to meet the computational requirements. The diagram must include: statements etc. …

Digital Electronics and Logic Design Tutorials - GeeksforGeeks

Mar 26, 2025 · In this Digital Electronics and Logic Design tutorial, we will dive deep into the fundamentals and advanced concepts like the Number System, Logic Gates, Boolean Algebra, …

How to Design a Digital Logic - EdrawMax Online

You can easily create a digital logic design within five simple steps. We will tell you the steps to develop a digital logic, a few essential tips, and which diagramming software is best for this job.

CircuitVerse - Online Digital Logic Circuit Simulator

From simple gates to complex sequential circuits, plot timing diagrams, automatic circuit generation, explore standard ICs, and much more. Export high-resolution images in multiple …

P1 Describe and illustrate fundamentals of Digital Logic Design 1 CLO:2 P3 Demonstrate the acquired knowledge to apply techniques related to the design and analysis of digital logic …

Students will learn principles of digital systems logic design and distinguish between analog and digital representations. They will be able to analyze a given combinational or sequential circuit …

–Keywords: Logic expression defining output, logic function, and input variable. –Let’s use two switches to control the lightbulb by connecting them in series and parallel. Ashutosh Trivedi …

Think of ALU as a number of other arithmetic and logic blocks in a single box! Function selects the block. ... ° Determine the 74HC382 ALU outputs for the following inputs: S2S1S0=010, …

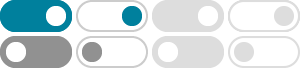

The basic buildings blocks of digital logic design are logic gates. A logic gate will accept one or more inputs, perform a logical operation and produce a single output as shown in figure 2.0.1. …

- Some results have been removed