• Eyeriss’ spatial architecture (basic tile, operand network) • ISAAC (analog) •Systolic arrays: dense compute units; data flows through these units with low rd/wr costs; loose connection …

Basic principle: Replace a single PE with a regular array of PEs and carefully orchestrate flow of data between the PEs Balance computation and memory bandwidth

Introduction to Linear Data Structures - GeeksforGeeks

Sep 22, 2023 · Linear data structures are commonly used for organising and manipulating data in a sequential fashion. Some of the most common linear data structures include: Arrays: A …

Systolic and wavefront arrays are determined by pipelining data concurrently with the (multi)processing - data and computational pipelining. Wavefront arrays use data-driven …

Types of systolic arrays • Early systolic arrays are linear arrays and one dimensional(1D) or two dimensional I/O(2D). • Most recently, systolic arrays are implemented as planar array with …

Systolic array architectures with same project vector and processor space vector, but different scheduling vectors can be derived from other transformations Edge reversal, associativity, …

Scalable linear array architectures for matrix inversion using

Feb 1, 2012 · In this paper, VLSI array architectures for matrix inversion are studied. A new binary-coded z -path (Bi-z) CORDIC is developed and implemented to compute the operations …

Most existing works focus on designing a linear array architecture for accelerating matrix multiplication on FPGAs. This paper towards the extension of this architecture by proposing a …

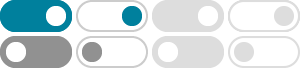

As depicted in Figure 1, a systolic array is often into a linear array, a two-dimensional rectangular mesh array, or sometimes, dimensional hexagonal mesh array. In a systolic array, every PE is …

We explore the design space for full-search vector quantizers and propose a novel linear processor array architecture in which global wiring is limited to clock and power supply …